SONY-CIS工艺|通过局部连接实现高全阱容量和低噪声特性

引言

我们在之前论文中介绍了SONY、OVT、ONSEMI、SAMUNG等各大Sensor厂商的CIS产品以及Sensor架构等,今天我们将借Sony发布的工艺改进的技术论文,介绍工艺的提升对于Pixel性能的影响。

该论文向我们展示了具有高全阱容量(FWC)和低随机噪声(RN)的2层晶体管像素堆叠CMOS图像传感器(CIS)的开发。通过在3D顺序集成工艺中在不同的硅(Si)层上制造PD和像素晶体管并引入单个垂直栅极(SVG)来增加光电二极管(PD)体积,从而实现了高FWC。引入了连接多个浮动扩散区(FD)和像素FinFET的掩埋亚局部连接(BSC),以提高转换增益和随机噪声(RN)。我们展示了一个0.6µm像素的2层像素,RN为0.99,FWC为8000e-,动态范围为78.1dB。

1. Introduction

确保像素收缩的高动态范围(Dynamic Range)对于图像捕获非常重要。像素收缩使得难以确保高FWC,这是由于像素晶体管的尺寸减小而不能确保PD区域和低噪声。双层晶体管像素堆叠CMOS图像传感器(“双层像素”)已被提出作为一种很有前途的技术,用于捕获低噪声和高D范围的图像,并在CMOS图像传感器中实现像素收缩。

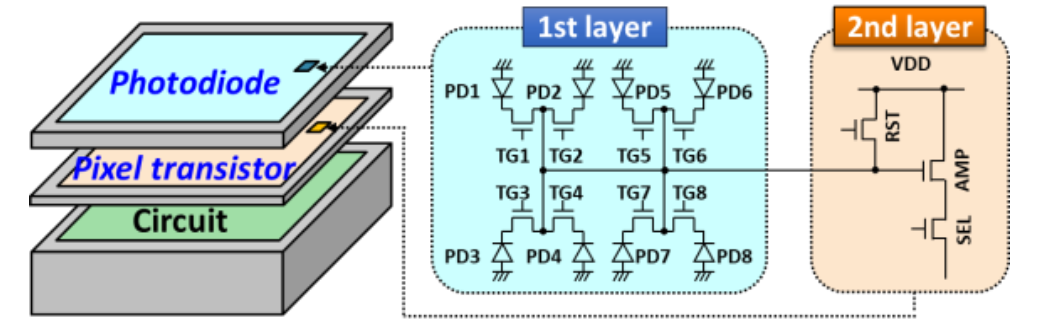

两层像素的示意图如下图所示:

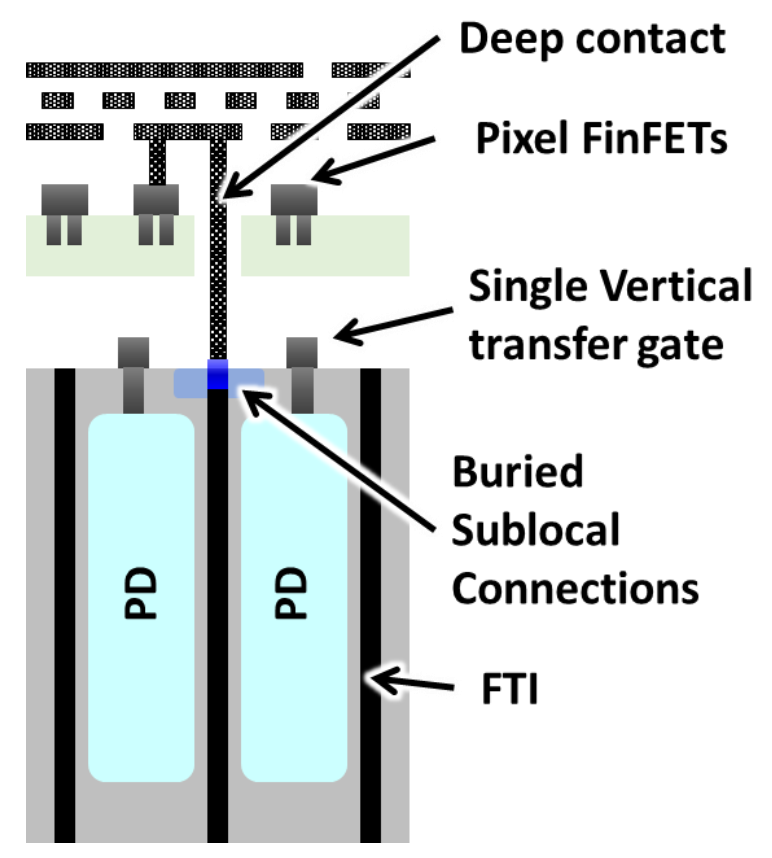

横截面示意图如下所示:

2层像素包括Si层,在该Si层上布置有PD和传输栅极。第二层包含t个像素晶体管,例如放大器晶体管、选择栅极、复位栅极和深接触,以连接PD和像素晶体管。此外,形成全沟槽隔离(FTI)以分离像素。在之前的研究中,我们开发了一种三维(3D)顺序集成过程来实现2层像素。

本文通过引入单个垂直传输门(SVG)、埋入式亚本地连接(BSC)和像素FinFET,提出了一种具有0.6µm像素的2层像素。

2 FWC提升

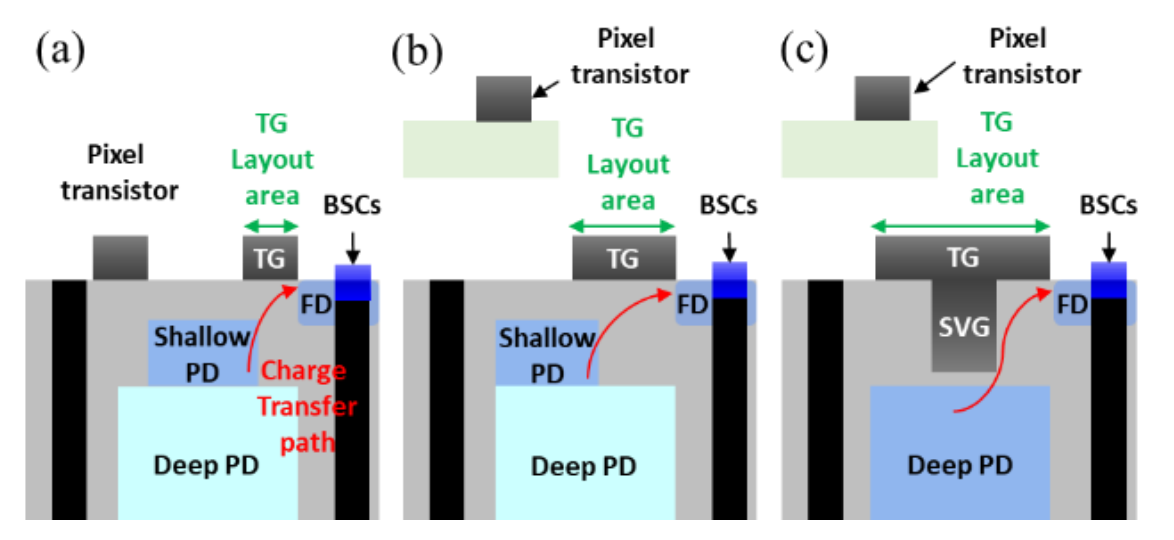

PD和传输门(TRG)的主要性能要求是高FWC,没有滞后和开花。在该器件中,通过在形成PD的第一Si层中引入全沟槽隔离(FTI)来完全分离PD,从而产生没有开花的结构。仅针对无滞后和FWC执行TRG优化,并且与不应用FTI的情况相比,提高了TRG设计的自由度。2层像素结构放大了TRG布局区域,如下图a-b所示:

SVG的引入扩大了可用于TRG放置的区域,因为它会导致PD配置的变化,从而消除了对浅PD的需要,从而实现高FWC和无滞后,如上图(b-c)所示。通过优化SVG的几何形状和位置,可以实现8000e-的FWC。

3 随机噪声提升

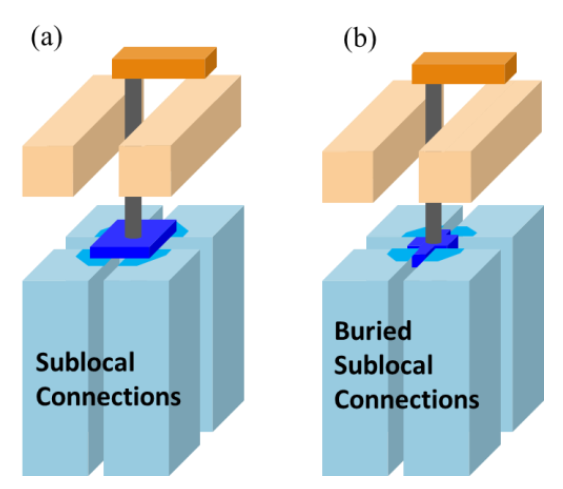

减小FD电容对于提高RN和转换增益是重要的。引入BSC以减少扩散层电容,引入像素FinFET以缩小FD共享单元。在传统的2层像素中,SC用于连接多个浮动扩散。SC是在第一层和第二层之间形成的结构,其与第一层的Si表面接触并具有欧姆导电性。

BSC是接触面积从Si表面变化到Si侧壁的结构,如下图b所示:

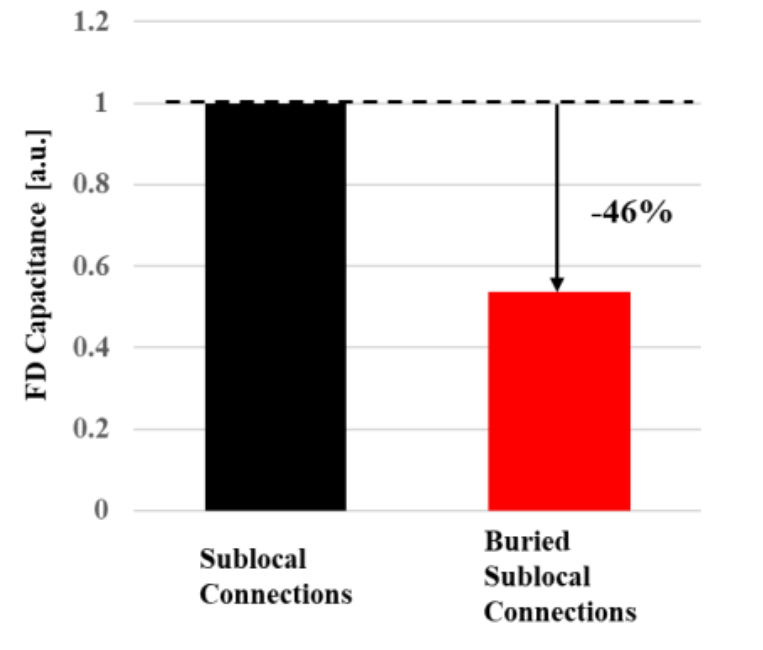

与SC相比,BSC可以与TGs分离,并且可以降低TGs的电容。通过优化BSC的布局和深度,FD电容减少了46%,如下图所示:

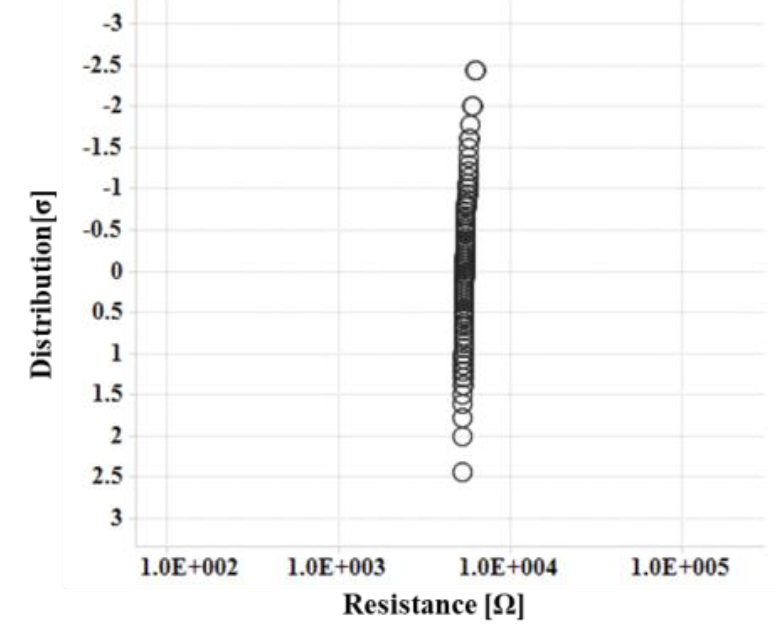

BSC表现出欧姆导电性,电阻特性如下图:

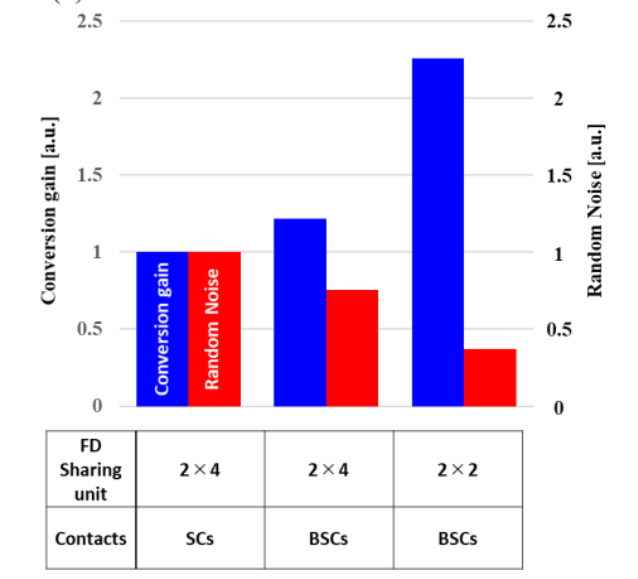

为了将FD共享单元从2x4缩小到2x2,我们采用了像素FinFET。引入BSC和改变FD共享单元使转换增益增加了2.26倍,RN减少了67%,如图所示(a)和(b):

| a | b |

|---|---|

|

|

4 结论

我们制造了一个0.6μm像素的2层像素,如下图所示:

![]()

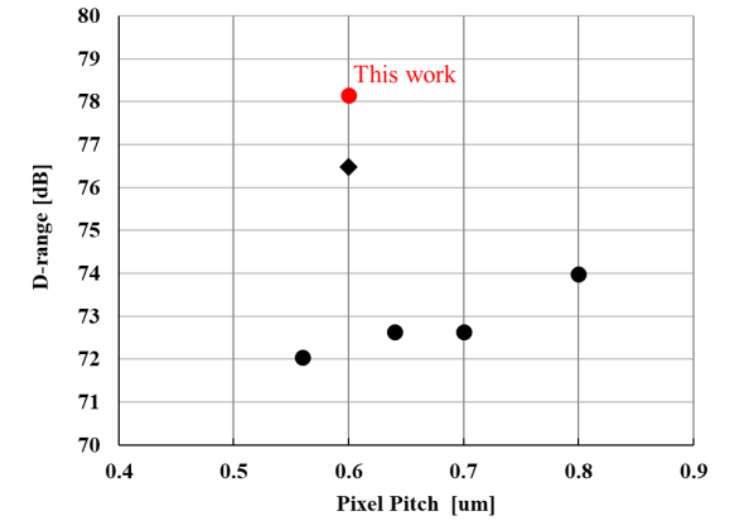

下图显示了像素大小和Drange之间的关系:

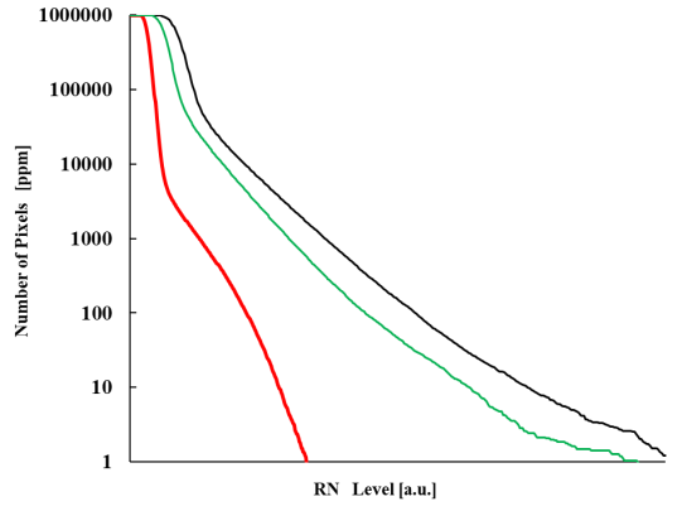

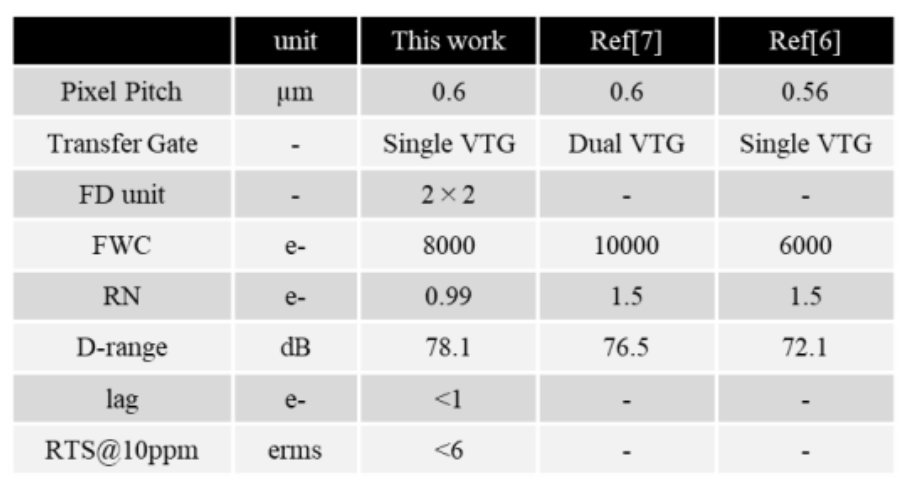

其中将先前研究中报道的PD CIS的FWC和RN与本研究中获得的进行了比较。表一总结了性能参数以及与先前研究的比较。

5 结束语

今天为大家介绍了Sony发布的工艺改进的技术论文,介绍工艺的提升对于Pixel性能的影响。希望对大家对于sensor工艺有着更深入了解与提升。

好了今天就到这里,希望今天可以给您带来对于传感器的更深的认知,喜欢的同学可以进行朋友圈分享以及点击文章在看。另外,对论文感兴趣的同学可以follow我的Github论文仓库AdasTechPapers,也可以加入知识星球以及交流群,获取一手行业资料~

加入星球:

如果您对ADAS感兴趣,欢迎关注我的公众号、知乎、Github、CSDN等,同时发表文章中使用源码以及文章会在我的GitHub进行开源,如果您有感兴趣话题也可以后台私信。