SPAD|SONY背面式的10µm SPAD像素阵列

引言

以下讲述了在300mm硅平台上通过90nm CMOS兼容工艺实现的现有技术的背照(BI)单光子雪崩二极管(SPAD)阵列传感器。该阵列由10µm像素组成,每个像素使用7µm厚的硅有源层,可以将设备的光学灵敏度扩展到近红外(NIR)光谱。此外,采用掩埋金属全沟槽隔离(FTI)来抑制串扰(Xtalk),这是器件中的一个关键特征,该器件足够敏感,可以由相邻像素发射的单个电致发光光子触发。最后,为了最大化填充因子(F.F)并允许BI结构,进行了Cu-Cu键合工艺。通过工艺和器件设计优化,不仅在λ=940nm时实现了大于14%的光子检测效率(PDE)和低定时抖动,而且与先前报道的SPAD传感器相比,实现了同类最佳的暗计数率(DCR)。这些组合功能为高效、眼睛安全和具有成本效益的飞行时间应用奠定了基础。

1. Introduction

单光子雪崩二极管(SPAD)作为一种实现光子计数的器件已经研究了多年。最近,直接飞行时间(dToF)已被用于支持AR/VR技术进入自动驾驶或智能手机,预计未来几年市场将大幅增长。这些应用的核心是SPAD阵列传感器,这是dToF所需的关键技术。目前,这种应用受到器件性能的限制,例如近红外(NIR)光谱中的低灵敏度或高暗计数率(DCR)。为了克服这些挑战,硅平台的选择是自然的,因为它确保了最先进的制造能力、高质量的材料和高工艺控制,从而进一步提高设备性能,并提供可靠且具有成本效益的深度传感器。

例如,让我们考虑像素缩放。作为一种在盖革模式下工作的芯片,SPAD在处理结构内的高电场时需要特别小心,这可以转化为保护环的使用,虽然很麻烦,但很有效。除此之外,如果考虑到读出电路所需的区域,该区域传统上与传感器位于同一平面上,则可以看出为什么SPAD阵列在填充因子(F.F,Fill Factor)和像素单元大小方面一直受到限制。这一困难可以通过向背照(BI)结构的过渡来克服,背照是经典CIS中的主流技术,其他小组已经报道了这一点,以实现高F.F SPAD阵列。简而言之,像素和电路在单独的晶片上实现,并最终通过Cu-Cu键合连接在一起。因此,读出电路最终位于像素下方,大大提高了F.F,从而提高了器件的灵敏度。

为了进一步提高器件在近红外光谱中的灵敏度,采用了三种主要策略。近红外光谱是硅吸收系数显著下降的光谱部分。首先,在像素级使用7µm的硅层,以确保足够长的光路。其次,在每个像素下插入一个金属反射器,以进一步扩展有效光路。最后,我们使用微透镜将尽可能多的光聚焦在每个像素内。在下文中,我们将更详细地解释这些选择如何转化为940nm处的高光子检测效率(PDE),并且我们将提出我们的方法来优化在这种器件中发现的PDE和定时抖动之间的折衷。

对于极高的增益,SPAD操作的另一个关键特征是抑制阵列中相邻像素之间的串扰(X-talk)。为了完全屏蔽每个像素免受寄生电或电致发光相关的X串扰的影响,采用了埋入式金属全沟槽隔离(FTI)。据我们所知,这是首次报道包括FTI的BI SPAD阵列。

2. Sensor架构

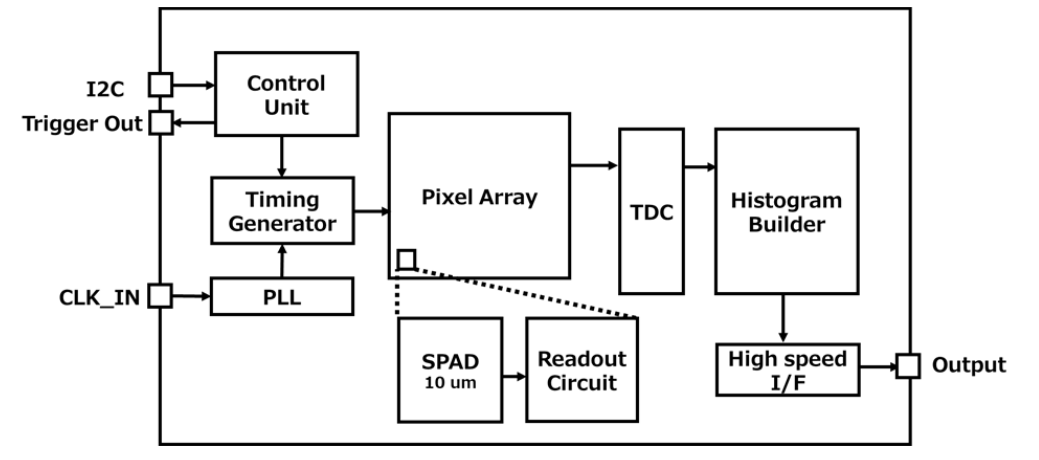

我们开发的dToF传感器的框图如下图所示:

一方面,使用90nm CMOS兼容工艺制造像素级晶片。另一方面,通过40nm CMOS兼容工艺实现了电路晶片。在Cu-Cu晶片接合之后,阵列中的每个SPAD像素连接到其自己的读出电路,该读出电路包括时间数字转换器(TDC)和直方图构建器。本质上,SPAD的检测时间是通过TDC测量的,然后直方图构建器允许对几个检测进行统计处理,以实现准确的飞行时间测量。包括读出电路在内的像素级的典型框图如图所示。2有效地允许飞行时间测量。请注意,淬火和再充电节点连接到SPAD的阴极端子。最后,信号输出被连接到另一个TDC。

3. BI SPAD

下图显示了SPAD像素的横截面:

![]()

传感部分位于顶部,与读出电路的连接位于底部,如Cu-Cu键合焊盘所示。如前所述,通过这种堆叠过程,F.F.大大提高。横截面进一步描绘了用作有源传感部件的厚7µm硅、微透镜和底部金属反射器,它们结合在一起,参与了PDE的增强。雪崩区域位于厚硅层的底部,设计用于通过雪崩击穿(二极管的盖革模式)放大载流子光生后的电流。此外,在像素的每一侧都可以看到隔离沟槽,清楚地展示了FTI,这使我们能够抑制前面所说的X谈话。

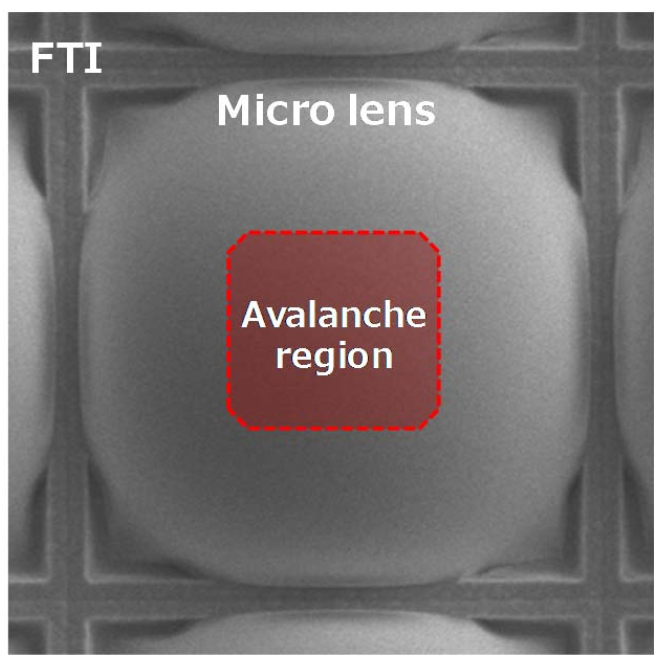

Sensor俯视图如下图所示:

其中Sensor的透镜设计得足够大,几乎完全覆盖像素,从而提供有效的光收集。

4. PDE以及时序抖动增强

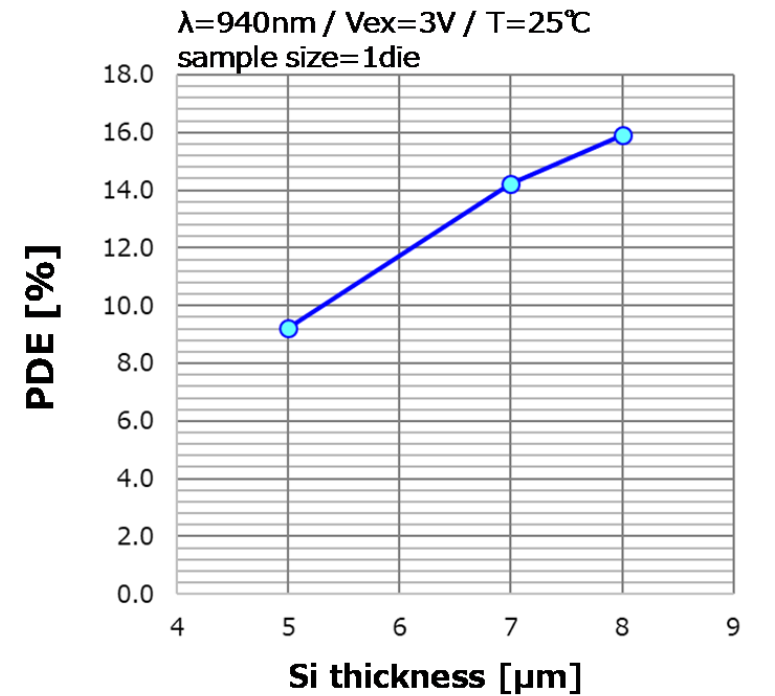

下图显示了不同硅厚度的PDE:

可以观察到,在所选择的范围内,PDE近似地以每微米硅2%的速率变化。这种相当敏感的依赖性与近红外中硅的低吸收系数有关。因此,在PDE方面,硅层越厚越好,因为光路增加,从而增加了光子吸收概率。

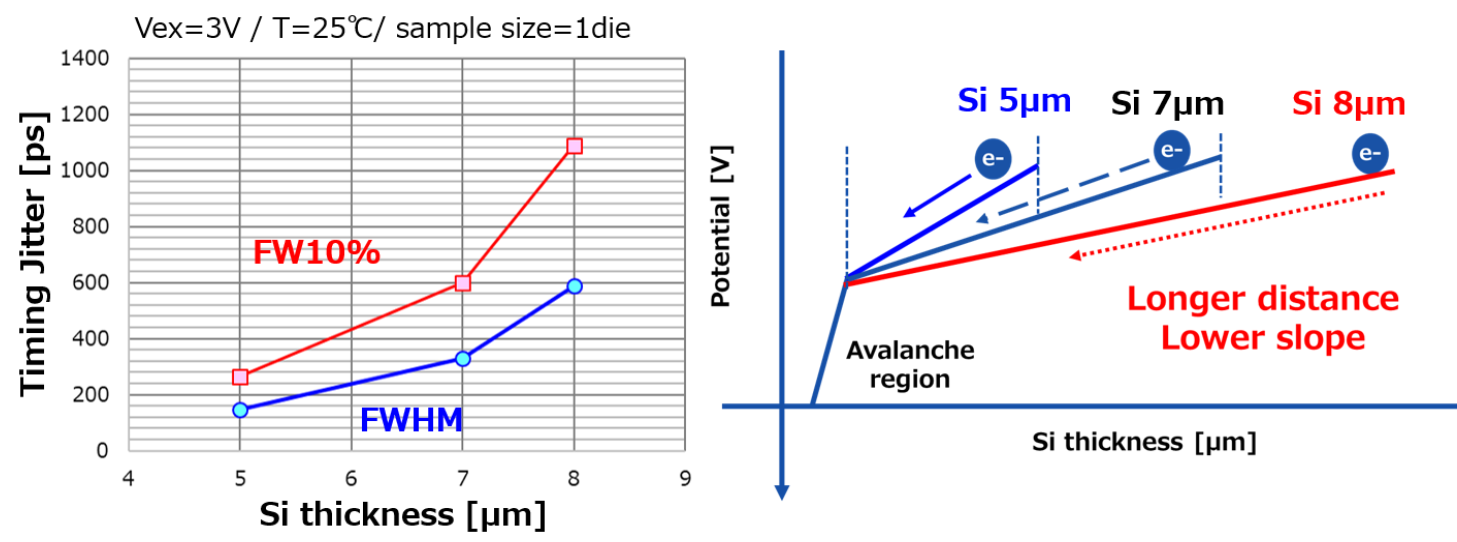

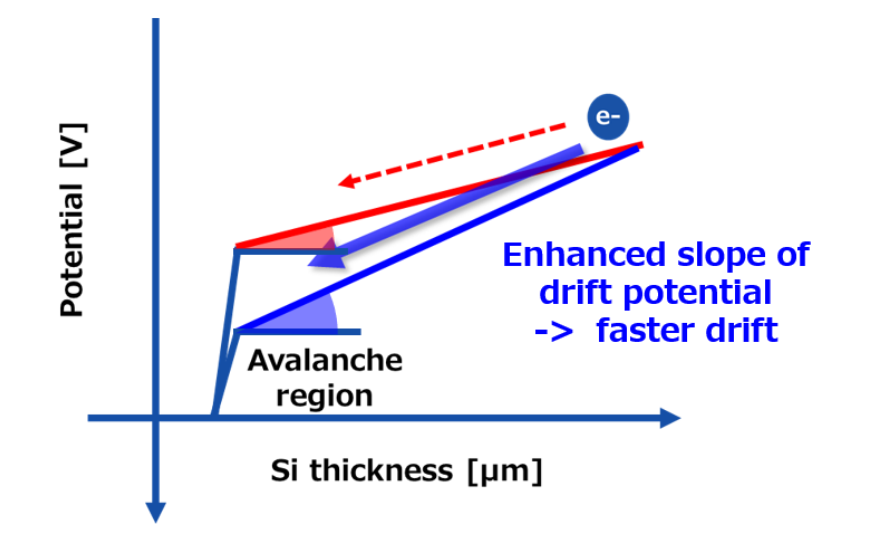

然而,增加硅厚度有一个重要的缺点。如图下图左所示,时序抖动随着硅厚度的增加而增加。我们参考下图右来说明潜在的机制。随着硅变得越来越厚,光生载流子到达雪崩区域所需的平均距离也会增加。不仅漂移长度增加,在固定偏置下漂移区域上的电压降不可避免地减小,这两个因素都会导致更长的定时抖动。

为了最大限度地利用这种权衡,在不影响击穿电压(VBD)也不改变过度偏置(Vex)的情况下,在设计漂移区的潜在景观时特别小心。下图从概念上表示了这一点。在实践中,这意味着同时设计和微调雪崩和漂移区域,以确保几乎恒定的VBD和Vex,而不会影响PDE和定时抖动。

5. Pixel性能

下图显示了NIR中的PDE依赖性:

![]()

所有测量均在室温下进行,Vex=3V。所开发的结构使我们能够在宽光谱范围内实现大的PDE,在850nm处的PDE为31.4%,在940nm处为14.2%。如此高的PDE使我们能够使用硅有效地扩展可用的3D深度感测范围,并提高现有技术的深度感测分辨率。还要注意,如果功耗高于性能,则可以通过减少读数的数量来实现低功耗飞行时间。

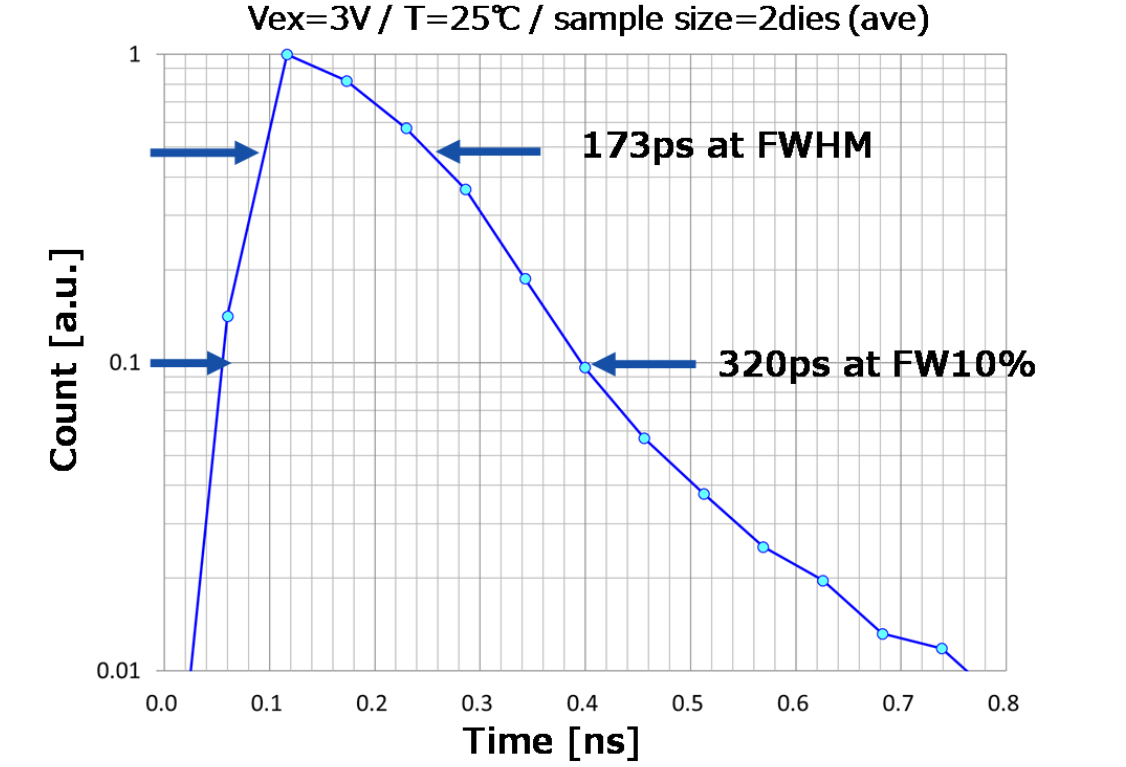

下图展示了一个典型的定时抖动直方图:

在室温下使用Vex=3V进行测量。测量的FW10%为320ps,FWHM为173ps,这两个值都是通过前面提到的优化漂移场获得的。

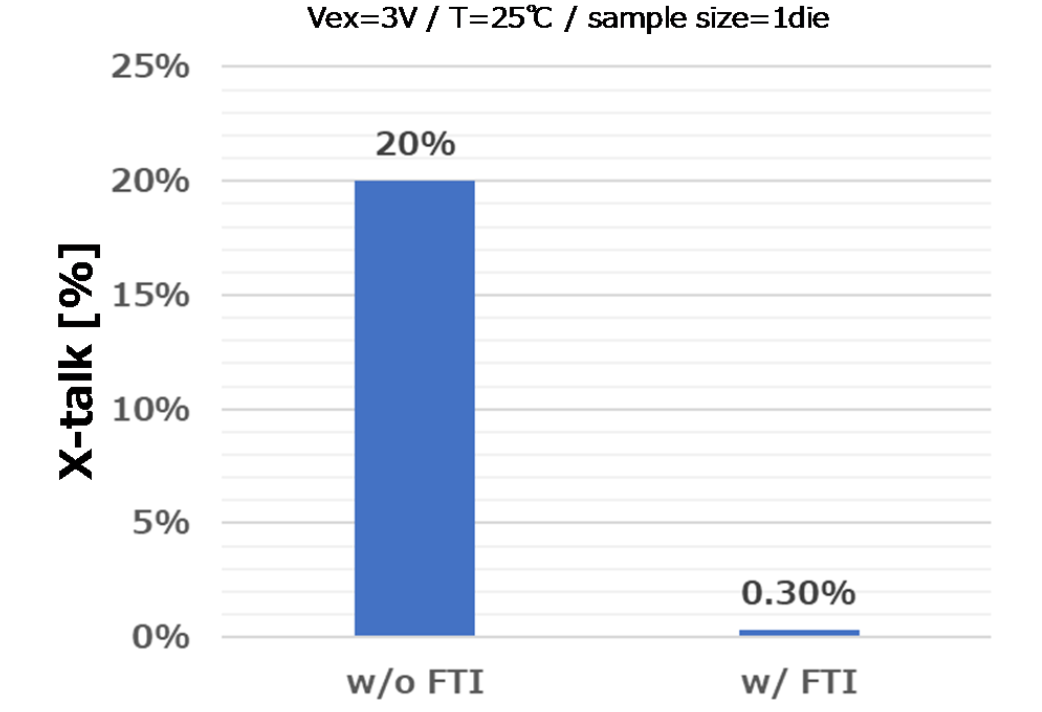

此外,FTI对X-talk的影响如下图所示:

可以看出,在没有FTI的情况下,X-talk高达20%。然而,通过使用FTI,我们能够将这个数字降低到0.3%,换句话说,使用从上到下的金属填充沟槽几乎完全抑制了它。

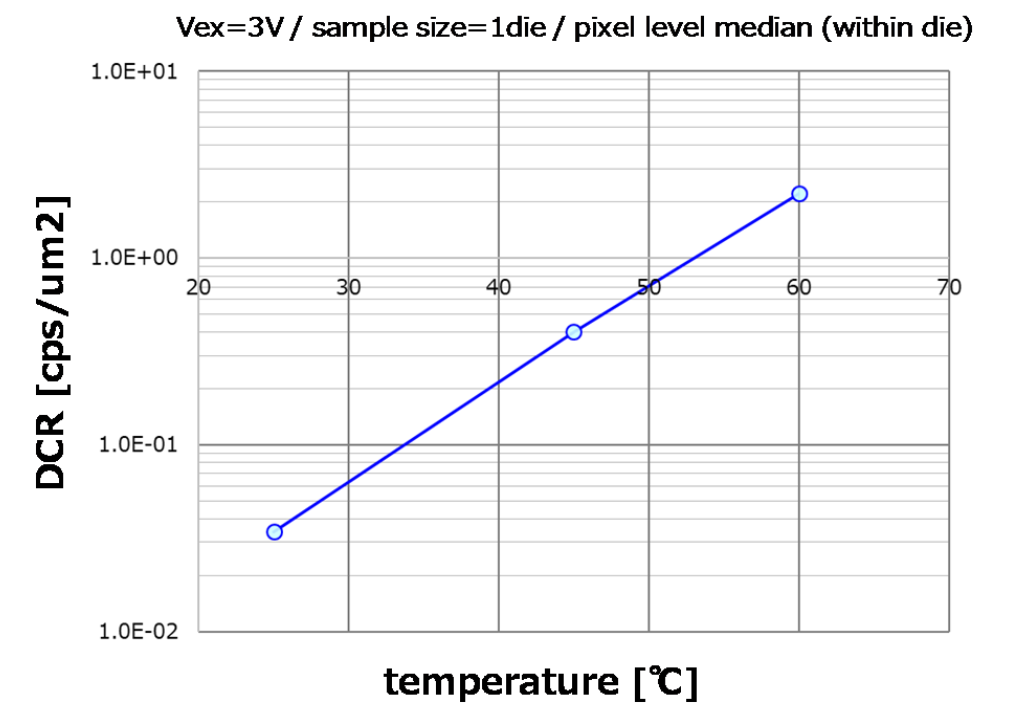

最后,DCR作为温度的函数如下图所示:

其中显示了每个芯片的中值DCR。即使在60°C下,DCR也低于2cps/µm2,与其他报道的SPAD架构相比,这是一个显著的改进。为了实现如此低的DCR值,开发了特定的工艺来减轻在整个工艺流程中在硅中产生的累积损伤。

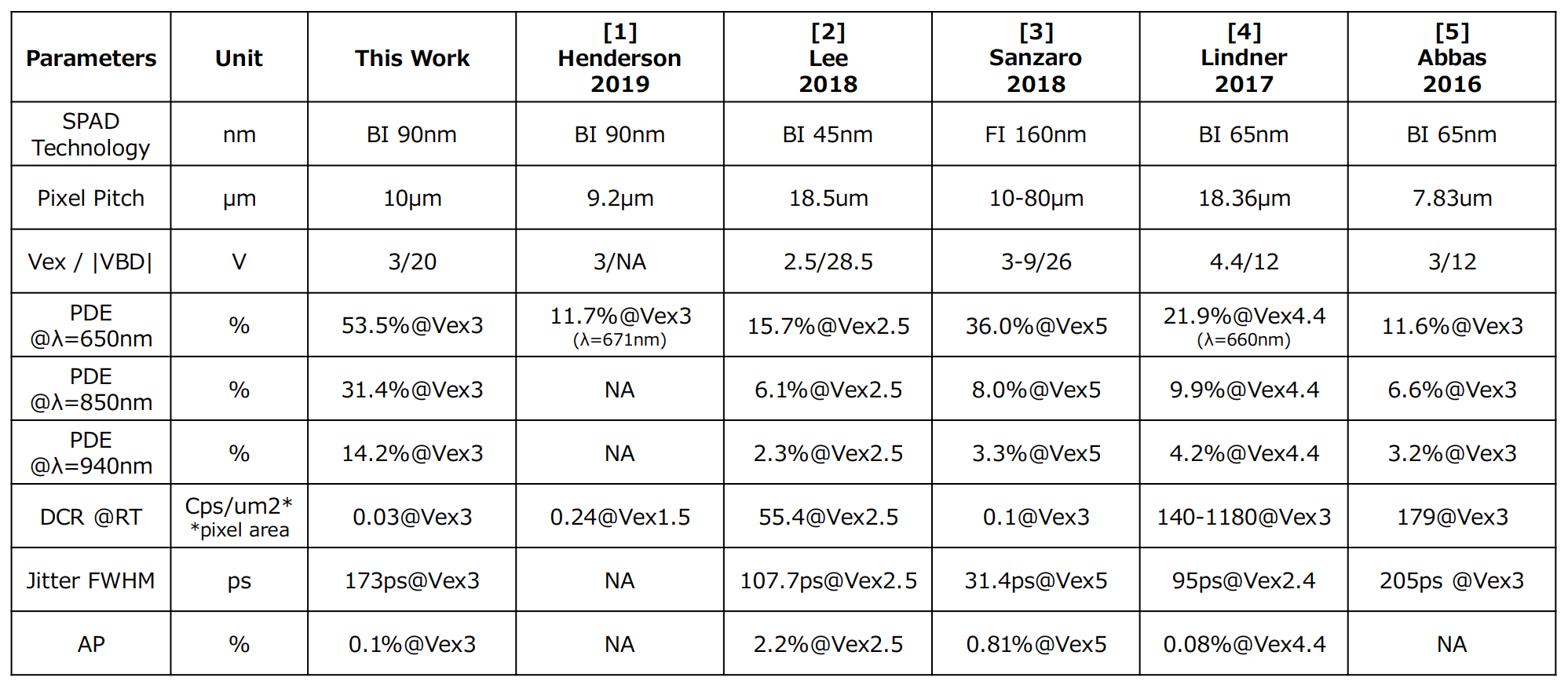

下表显示了所开发的SPAD阵列传感器的总体性能,并将其与之前报道的硅基SPAD阵列感应器进行了比较。

6. 结束语

我们开发了一种最先进的BI 10µm SPAD阵列传感器,采用90nm CMOS兼容工艺,包括掩埋金属FTI和Cu-Cu键合。据报道,使用7µm厚的硅层、传感器内的微调电势景观和专用工艺、940nm波长下超过14%的高PDE和超低DCR。通过结构优化,还证明了低定时抖动、难以在不恶化PDE的情况下进行改进以及抑制了X串扰。

好了今天就到这里,本文为大家介绍了Sony SPAD传感器的技术细节,希望今天可以给您带来对于传感器的更深的认知,喜欢的同学可以进行朋友圈分享以及点击文章在看。另外,对论文感兴趣的同学可以follow我的Github论文仓库,也可以加入知识星球以及交流群,获取一手行业资料~

加入星球:

如果您对ADAS感兴趣,欢迎关注我的公众号、知乎、Github、CSDN等,同时发表文章中使用源码以及文章会在我的GitHub进行开源,如果您有感兴趣话题也可以后台私信。